# POLITECNICO DI TORINO ESAMI DI STATO PER L'ABILITAZIONE ALL'ESERCIZIO DELLA PROFESSIONE DI INGEGNERE DELL'INFORMAZIONE

# I Sessione 2019 - Sezione A Settore dell'Informazione

## Prova PRATICA del 23 luglio 2019

Il Candidato svolga uno a scelta fra i seguenti temi proposti. Gli elaborati prodotti dovranno essere stilati in forma chiara, ordinata, sintetica e leggibile. La completezza, l'attinenza e la chiarezza espositiva costituiranno elementi di valutazione.

#### Tema n. 1

Il candidato progetti un sistema per il controllo e la regolazione di un motore elettrico a corrente continua.

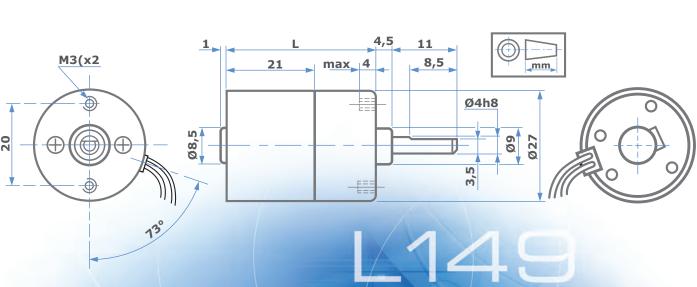

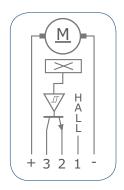

Il motore è un L149.12.43 della Micromotors, caratterizzato da un'alimentazione nominale di 12 V, velocità nominale di 60 RPM, rapporto di riduzione di 43,3:1 e momento di inerzia  $J=1.1\cdot10^{-5}kg\cdot m^2$  (datasheet in allegato). Inoltre, il motore include un sensore a effetto Hall e i relativi circuiti di condizionamento, che permettono di generare in uscita tre impulsi per rotazione (datasheet in allegato). Dalle misure effettuate, l'induttanza e la resistenza del motore sono  $R=89~\Omega~e~L=79~mH$ .

Si richiede il progetto del circuito di controllo della velocità del motore tramite la tecnica della modulazione a larghezza di impulso (PWM). In particolare, si faccia riferimento all'ipotesi in cui il motore non sia collegato ad alcun carico meccanico.

Per fornire i necessari livelli di tensione da applicare al motore, si può usare un driver opportuno, come per esempio l'L293 della Texas Instruments (datasheet in allegato).

Il sistema deve operare in due diverse modalità di funzionamento:

- 1. A anello aperto, con velocità minima pari a zero e massima pari a 4 rad/s. La velocità istantanea a vuoto deve essere proporzionale al valore binario su otto bit, letto da una porta di ingresso.

- 2. A anello chiuso in retroazione. In questo caso, il sistema legge l'effettiva velocità di rotazione del motore tramite il sensore a effetto Hall, misura la differenza rispetto alla velocità impostata sulla porta di ingresso e usa un controllo integrativo per regolare il motore.

La modalità di funzionamento e la direzione di rotazione sono imposte mediante due pulsanti esterni.

Per la realizzazione della parte digitale del sistema, il candidato ha a disposizione due opzioni:

- 1. Un microcontrollore, come l'STM32F4 (manuale allegato)

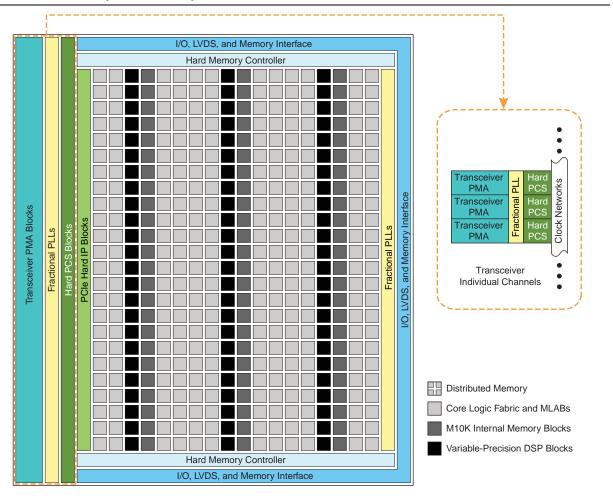

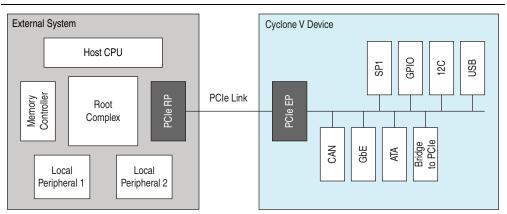

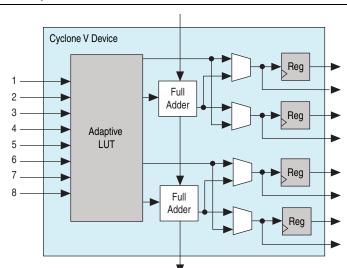

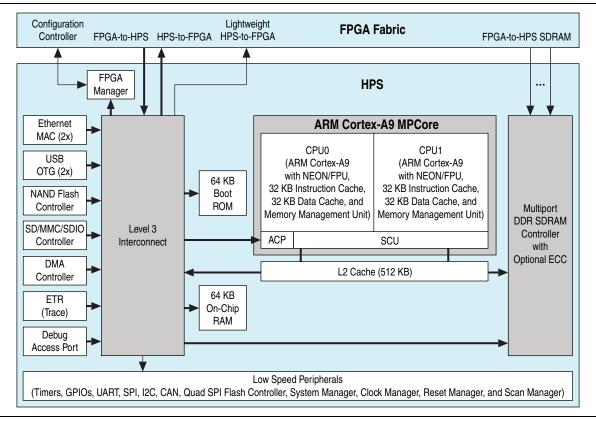

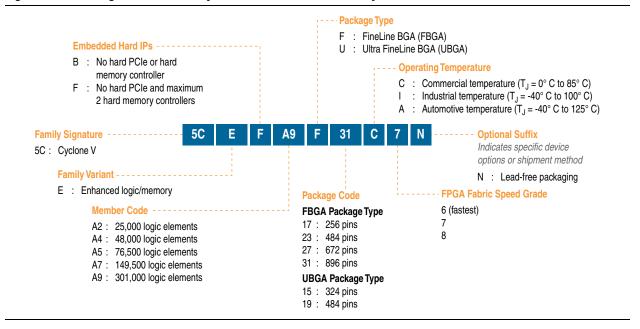

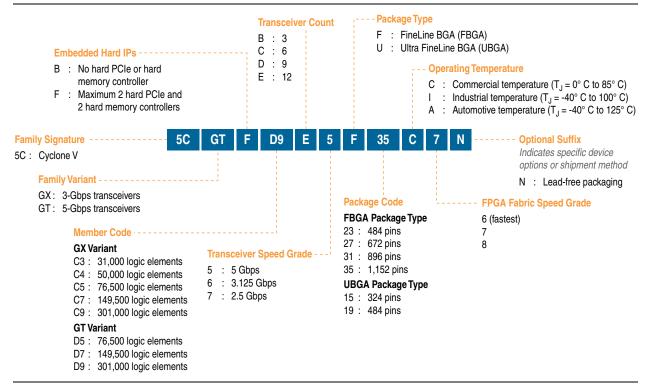

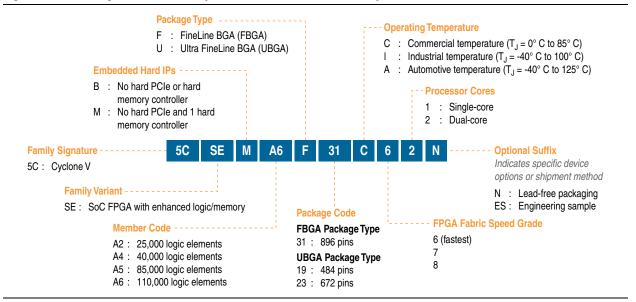

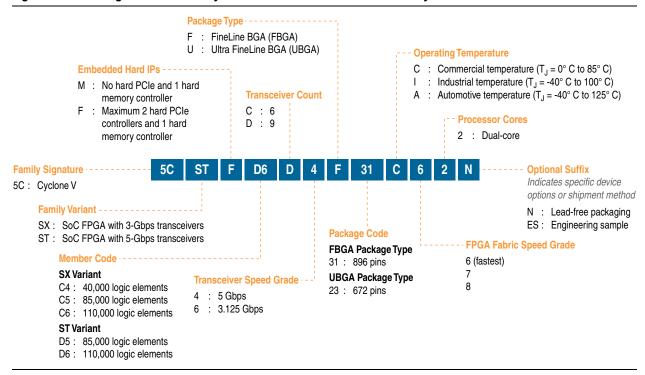

- 2. Un dispositivo FPGA, come il Cyclone V (datasheet allegato)

Seque Tema 1 >>>

#### È richiesto al candidato di:

- scegliere una delle due opzioni,

- progettare il circuito di alimentazione del controllore digitale (microcontrollore/FPGA), del driver e del sensore a effetto Hall a partire dalla rete elettrica 230V, 50Hz,

- progettare l'elettronica di interfaccia tra il microcontrollore (o la FPGA) e il motore nelle due modalità di funzionamento, dimensionando i componenti passivi necessari e dettagliando le specifiche di eventuali altre unità.

- progettare l'interfaccia tra il sensore ad effetto Hall e il microcontrollore/FPGA,

- fornire uno schema a blocchi dettagliato dell'intero sistema,

- derivare le equazioni per la regolazione della velocità del motore in PWM.

Il candidato, inoltre, completi il progetto sulla base della scelta effettuata: nel primo caso, fornisca il codice C per la configurazione del microcontrollore, la gestione delle periferiche utilizzate (in polling o in interrupt) e l'esecuzione dell'intera applicazione. Nel secondo caso, fornisca invece la vista a livello RTL (Register Transfer Level) dell'architettura digitale da sintetizzare sulla FPGA e il codice VHDL per i principali componenti allocati. Si privilegino scelte di progetto che minimizzino i costi produttivi e massimizzino l'efficienza energetica.

Per le scelte di progetto lasciate libere e i dati non esplicitamente riportati nel testo si ricorra a ragionevoli e giustificate ipotesi.

#### Materiale in consultazione:

- All. 1: Datasheet del motore (L149.12.43, della Micromotors)

- All. 2: Datasheet del sensore ad effetto Hall

- All. 3: Datasheet del driver L293

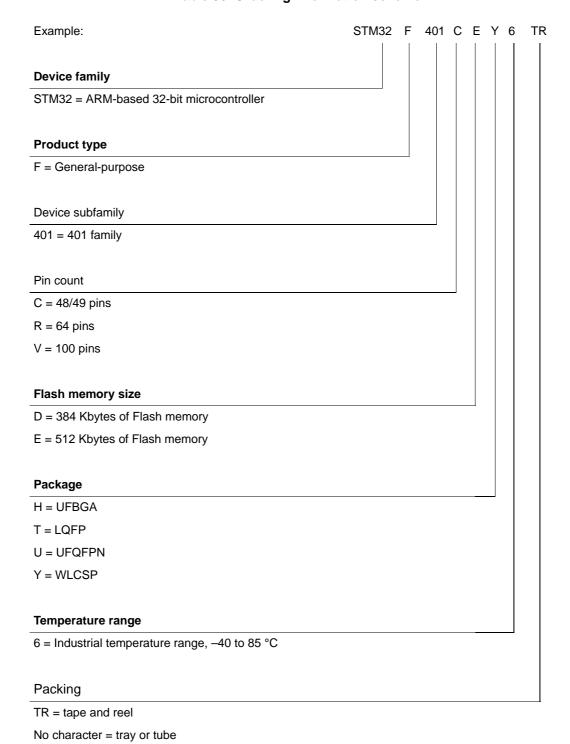

- All. 4: Datasheet del microcontrollore STM32F401

- All. 5: Reference manual del microcontrollore STM32F4 (RM0368)

- All. 6: Datasheet del dispositivo Cyclone V

# DATI TECNICI

# TECHNICAL

i

Soppressione disturbi con VDR sul collettore Spazzole in metallo prezioso (Au - Ag - Cu) Direzione di rotazione secondo polarità Può essere montato in ogni posizione Massimo carico radiale: 10N

Massimo carico assiale: 5N Temperatura di esercizio: -20°C/60°C

Peso approssimativo: 55g

VDR interference suppression on the collector Precious metal brushes (Au - Ag - Cu) Direction of rotation depending on polarity Can be mounted in any position Maximum radial shaft load: 10N Maximum axial shaft load: 5N Temperature range: -20°C/60°C

Approx weight: 55g

Valori tipici a temperatura ambiente +20° Tolleranza +/- 10% Typical values at ambient temperature +20° Tolerance +/- 10%

|                         |                                 |    |                |                    | VELOCITÁ<br>SPEED |                           |                   |                           |  |

|-------------------------|---------------------------------|----|----------------|--------------------|-------------------|---------------------------|-------------------|---------------------------|--|

| TIPO<br>TYPE            | TENSIONE<br>NOMINALE<br>NOMINAL | L  | RAPPORTO<br>:1 | COPPIA<br>NOMINALE | SENZA<br>CARICO   | CON<br>COPPIA<br>NOMINALE | SENZA<br>CARICO   | CON<br>COPPIA<br>NOMINALE |  |

| TIPE                    | VOLTAGE                         |    | RATIO<br>TO:1  | NOMINAL<br>TORQUE  | NO<br>LOAD        | AT<br>NOMINAL<br>TORQUE   | NO<br>LOAD        | AT<br>NOMINAL<br>TORQUE   |  |

|                         | V                               | mm |                | Ncm                | ı                 | rpm                       |                   | mA                        |  |

| 4<br>L149· 6·10<br>12   | 4,5<br>6<br>12                  | 36 | 10             | 1,5                | 255<br>215<br>255 | 165<br>120<br>165         | <35<br><30<br><20 | 100<br>85<br>50           |  |

| 4<br>L149· 6 ·21<br>12  | 4,5<br>6<br>12                  | 36 | 20,8           | 2,5                | 125<br>105<br>125 | 80<br>60<br>80            | <35<br><30<br><20 | 100<br>85<br>50           |  |

| 4<br>L149· 6·43<br>12   | 4,5<br>6<br>12                  | 41 | 43,3           | 3,8                | 60<br>52<br>60    | 40<br>32<br>40            | <35<br><30<br><20 | 100<br>85<br>50           |  |

| 4<br>L149· 6·90<br>12   | 4,5<br>6<br>12                  | 41 | 90,3           | 8                  | 30<br>25<br>30    | 18<br>13<br>18            | <35<br><30<br><20 | 100<br>85<br>50           |  |

| 4<br>L149· 6·188<br>12  | 4,5<br>6<br>12                  | 46 | 188            | 14                 | 14<br>12<br>14    | 9<br>7<br>9               | <35<br><30<br><20 | 100<br>85<br>50           |  |

| 4<br>L149· 6 ·392<br>12 | 4,5<br>6<br>12                  | 46 | 391,8          | 20                 | 7<br>6<br>7       | 5<br>4<br>5               | <35<br><30<br><20 | 90<br>75<br>45            |  |

Viale Piave, 80/82 - 23879 VERDERIO (LC) ITALY Tel. 039.510611-499 Fax 039.513617 motors.s. | www.micromotors.eu - info@micromotors.eu

# gear-motors with Hall-effect encoder

#### SIX POLES MAGNET: THREE PULSES FOR MOTOR TURN

#### HALL-EFFECT SWITCHES

Hall-effect switches are highly temperature stable and stress-resistant sensors best utilized in applications that provide steep magnetic slopes and low residual levels of magnetic flux density. Each device includes a voltage regulator. quadratic Hall voltage generator. temperature stability circuit. signal chopper stabilized amplifier. Schmitt trigger and an open drain mosfet on a single silicon chip.

The on-board regulator permits operation with supply voltages of 3.5 to 24V. The output mosfet can sink up to 20 mA with suitable output pull up. they can be used directly with bipolar or MOS logic circuits.

#### connections

+ Red : +Motor

3 Blue : O.C. Output

2 Green : Ground

1 Brown : Vcc (Hall)

- Black : -Motor

| ABSOLUTE MAX                 | ABSOLUTE MAXIMUM RATINGS |            |       |  |  |  |  |

|------------------------------|--------------------------|------------|-------|--|--|--|--|

| PARAMETER                    | SYMBOL                   | VALUE      | UNITS |  |  |  |  |

| Supply Voltage               | VDD                      | 28         | V     |  |  |  |  |

| Supply Current               | IDD                      | 50         | mA    |  |  |  |  |

| Output Voltage               | VOUT                     | 28         | V     |  |  |  |  |

| Output Current               | IOUT                     | 50         | mA    |  |  |  |  |

| Storage Temperature Range    | TS                       | -50 to 150 | °C    |  |  |  |  |

| Maximum Junction Temperature | TJ                       | 2.0        | °C    |  |  |  |  |

Exceeding the absolute maximum ratings may cause permanent damage. Exposure to all absolute-maximum-rated conditions for extended periods may affect device reliability.

| GENERAL I                 | ELECTI | RICAL SPECIF                                                                   | ICA | TIO  | N S |       |

|---------------------------|--------|--------------------------------------------------------------------------------|-----|------|-----|-------|

| PARAMETER                 | SYMBOL | TEST CONDITIONS                                                                | MIN | TYPE | MAX | UNITS |

| Supply Voltage            | VDD    | Operating                                                                      | 3.5 | -    | 24  | V     |

| Supply Current            | IDD    | B <brp< td=""><td>-</td><td>-</td><td>5</td><td>mA</td></brp<>                 | -   | -    | 5   | mA    |

| Output Saturation Voltage | VDSon  | IOUT=20mA. B>BOP                                                               | -   | -    | 0.5 | V     |

| Output Leakage Current    | IOFF   | IB <brp. vout="24V&lt;/td"><td>-</td><td>0.3</td><td>10</td><td>μΑ</td></brp.> | -   | 0.3  | 10  | μΑ    |

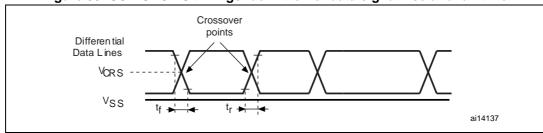

| Output Rise Time          | tr     | RL=1kΩ. CL=20pF                                                                | -   | 0.25 | -   | μs    |

| Output Fall Time          | tr     | RL=1k $\Omega$ . CL=20pF                                                       | -   | 0.25 | -   | μs    |

OC Operating Parameters TA = 25 °C, VDD = 3.5V to 24V (unless otherwise specified)

technology in motion

Page 16

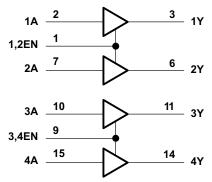

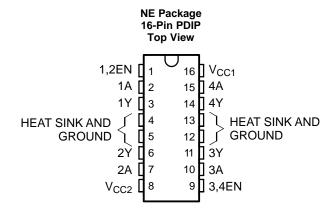

L293, L293D

SLRS008D - SEPTEMBER 1986 - REVISED JANUARY 2016

# L293x Quadruple Half-H Drivers

#### **Features**

- Wide Supply-Voltage Range: 4.5 V to 36 V

- Separate Input-Logic Supply

- Internal ESD Protection

- High-Noise-Immunity Inputs

- Output Current 1 A Per Channel (600 mA for L293D)

- Peak Output Current 2 A Per Channel (1.2 A for

- Output Clamp Diodes for Inductive Transient Suppression (L293D)

## **Applications**

- Stepper Motor Drivers

- DC Motor Drivers

- Latching Relay Drivers

## 3 Description

The L293 and L293D devices are quadruple highcurrent half-H drivers. The L293 is designed to provide bidirectional drive currents of up to 1 A at voltages from 4.5 V to 36 V. The L293D is designed to provide bidirectional drive currents of up to 600-mA at voltages from 4.5 V to 36 V. Both devices are designed to drive inductive loads such as relays, solenoids, DC and bipolar stepping motors, as well as other high-current/high-voltage loads in positivesupply applications.

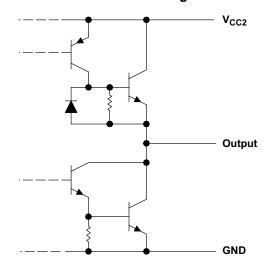

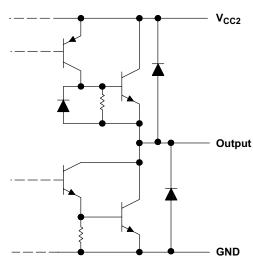

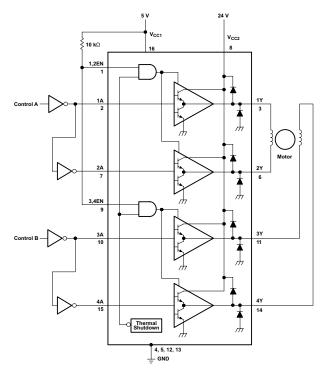

Each output is a complete totem-pole drive circuit, with a Darlington transistor sink and a pseudo-Darlington source. Drivers are enabled in pairs, with drivers 1 and 2 enabled by 1,2EN and drivers 3 and 4 enabled by 3,4EN.

The L293 and L293D are characterized for operation from 0°C to 70°C.

#### Device Information<sup>(1)</sup>

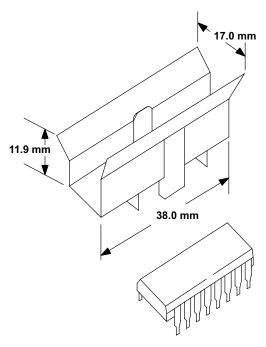

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)    |

|-------------|-----------|--------------------|

| L293NE      | PDIP (16) | 19.80 mm × 6.35 mm |

| L293DNE     | PDIP (16) | 19.80 mm × 6.35 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Logic Diagram**

# **Table of Contents**

| 1 | Features 1                           |    | 8.3 Feature Description                          | <mark>7</mark> |

|---|--------------------------------------|----|--------------------------------------------------|----------------|

| 2 | Applications 1                       |    | 8.4 Device Functional Modes                      | 8              |

| 3 | Description 1                        | 9  | Application and Implementation                   | 9              |

| 4 | Revision History2                    |    | 9.1 Application Information                      | 9              |

| 5 | Pin Configuration and Functions      |    | 9.2 Typical Application                          | 9              |

| 6 | Specifications4                      |    | 9.3 System Examples                              | 10             |

| • | 6.1 Absolute Maximum Ratings 4       | 10 | Power Supply Recommendations                     | 13             |

|   | 6.2 ESD Ratings                      | 11 | Layout                                           | 14             |

|   | 6.3 Recommended Operating Conditions |    | 11.1 Layout Guidelines                           | 14             |

|   | 6.4 Thermal Information              |    | 11.2 Layout Example                              | 14             |

|   | 6.5 Electrical Characteristics5      | 12 | Device and Documentation Support                 | 15             |

|   | 6.6 Switching Characteristics 5      |    | 12.1 Related Links                               | 15             |

|   | 6.7 Typical Characteristics 5        |    | 12.2 Community Resources                         | 15             |

| 7 | Parameter Measurement Information 6  |    | 12.3 Trademarks                                  | 15             |

| 8 | Detailed Description 7               |    | 12.4 Electrostatic Discharge Caution             | 15             |

| • | 8.1 Overview                         |    | 12.5 Glossary                                    | 15             |

|   | 8.2 Functional Block Diagram         | 13 | Mechanical, Packaging, and Orderable Information | 15             |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision C (November 2004) to Revision D                                                                                                                                                             | Page |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Removed Ordering Information table                                                                                                                                                                               | 1    |

| • | Added ESD Ratings and Thermal Information tables, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and |      |

|   | Documentation Support section, and Mechanical, Packaging, and Orderable Information section                                                                                                                      | 1    |

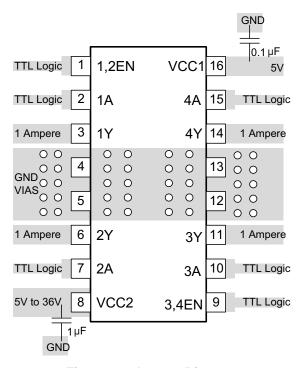

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN              |              | TYPE                             | DESCRIPTION                                                                                             |  |  |

|------------------|--------------|----------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| NAME             | NO.          | TIPE                             | DESCRIPTION                                                                                             |  |  |

| 1,2EN            | 1            | I                                | Enable driver channels 1 and 2 (active high input)                                                      |  |  |

| <1:4>A           | 2, 7, 10, 15 | 15 I Driver inputs, noninverting |                                                                                                         |  |  |

| <1:4>Y           | 3, 6, 11, 14 | 0                                | Driver outputs                                                                                          |  |  |

| 3,4EN            | 9            | I                                | Enable driver channels 3 and 4 (active high input)                                                      |  |  |

| GROUND           | 4, 5, 12, 13 | _                                | Device ground and heat sink pin. Connect to printed-circuit-board ground plane with multiple solid vias |  |  |

| V <sub>CC1</sub> | 16           | _                                | 5-V supply for internal logic translation                                                               |  |  |

| V <sub>CC2</sub> | 8            | _                                | Power VCC for drivers 4.5 V to 36 V                                                                     |  |  |

Copyright © 1986–2016, Texas Instruments Incorporated

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                        | MIN  | MAX                  | UNIT |

|------------------------------------------------------------------------|------|----------------------|------|

| Supply voltage, V <sub>CC1</sub> <sup>(2)</sup>                        |      | 36                   | V    |

| Output supply voltage, V <sub>CC2</sub>                                |      | 36                   | V    |

| Input voltage, V <sub>I</sub>                                          |      | 7                    | V    |

| Output voltage, V <sub>O</sub>                                         | -3   | V <sub>CC2</sub> + 3 | V    |

| Peak output current, I <sub>O</sub> (nonrepetitive, t ≤ 5 ms): L293    | -2   | 2                    | Α    |

| Peak output current, I <sub>O</sub> (nonrepetitive, t ≤ 100 μs): L293D | -1.2 | 1.2                  | Α    |

| Continuous output current, I <sub>O</sub> : L293                       | -1   | 1                    | Α    |

| Continuous output current, I <sub>O</sub> : L293D                      | -600 | 600                  | mA   |

| Maximum junction temperature, T <sub>J</sub>                           |      | 150                  | °C   |

| Storage temperature, T <sub>stg</sub>                                  | -65  | 150                  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                   |                         |                                                                     | VALUE | UNIT |

|-------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| \/                |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 | \/   |

| V <sub>(ESI</sub> | <sup>D)</sup> discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                |                                                                         | MIN                 | NOM MAX          | UNIT |

|-----------------|--------------------------------|-------------------------------------------------------------------------|---------------------|------------------|------|

|                 | Supply voltage                 | V <sub>CC1</sub>                                                        | 4.5                 | 7                | \/   |

|                 | Supply voltage                 | $V_{CC1}$ $V_{CC2}$ $V_{CC1} \le 7 \text{ V}$ $V_{CC1} \ge 7 \text{ V}$ | V <sub>CC1</sub>    | 36               | V    |

| .,              | High level inner wells as      | V <sub>CC1</sub> ≤ 7 V                                                  | 2.3                 | V <sub>CC1</sub> | V    |

| V <sub>IH</sub> | High-level input voltage       | V <sub>CC1</sub> ≥ 7 V                                                  | 2.3                 | 7                | V    |

| V <sub>IL</sub> | Low-level output voltage       |                                                                         | -0.3 <sup>(1)</sup> | 1.5              | V    |

| T <sub>A</sub>  | Operating free-air temperature |                                                                         | 0                   | 70               | °C   |

<sup>(1)</sup> The algebraic convention, in which the least positive (most negative) designated minimum, is used in this data sheet for logic voltage levels.

#### 6.4 Thermal Information

|                        |                                              | L293, L293D |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | NE (PDIP)   | UNIT |

|                        |                                              | 16 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance (2)   | 36.4        | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 22.5        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 16.5        | °C/W |

| Ψлτ                    | Junction-to-top characterization parameter   | 7.1         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 16.3        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Copyright © 1986–2016, Texas Instruments Incorporated

<sup>(2)</sup> All voltage values are with respect to the network ground terminal.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> The package thermal impedance is calculated in accordance with JESD 51-7.

#### 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                      |    | •                        | TEST CONDITIONS                  | MIN                    | TYP                    | MAX  | UNIT |

|------------------|--------------------------------|----|--------------------------|----------------------------------|------------------------|------------------------|------|------|

| .,               |                                |    | L293: I <sub>OH</sub> =  | -1 A                             | V <sub>CC2</sub> – 1.8 |                        |      | .,   |

| V <sub>OH</sub>  | High-level output voltage      |    | L293D: I <sub>OH</sub>   | L293D: I <sub>OH</sub> = - 0.6 A |                        | V <sub>CC2</sub> – 1.4 |      | V    |

|                  | V Low level output voltage     |    | L293: I <sub>OL</sub> =  | 1 A                              |                        | 4.0                    | 4.0  |      |

| $V_{OL}$         | Low-level output voltage       |    | L293D: I <sub>OL</sub> : | = 0.6 A                          |                        | 1.2                    | 1.8  | V    |

| V <sub>OKH</sub> | High-level output clamp voltag | е  | L293D: I <sub>OK</sub>   | = -0.6 A                         |                        | V <sub>CC2</sub> + 1.3 |      | V    |

| V <sub>OKL</sub> | Low-level output clamp voltage | Э  | L293D: I <sub>OK</sub>   | L293D: I <sub>OK</sub> = 0.6 A   |                        | 1.3                    |      | V    |

|                  | High level innut gurrent       | Α  | \/ 7\/                   |                                  |                        | 0.2                    | 100  |      |

| I <sub>IH</sub>  | High-level input current       | EN | v <sub>1</sub> = 7 v     | V <sub>I</sub> = 7 V             |                        | 0.2                    | 10   | μΑ   |

|                  | Laurent Samuel aumanet         | А  | V 0                      |                                  |                        | -3                     | -10  |      |

| I <sub>IL</sub>  | Low-level input current        | EN | V <sub>1</sub> = 0       | $V_1 = 0$                        |                        | -2                     | -100 | μΑ   |

|                  |                                |    |                          | All outputs at high level        |                        | 13                     | 22   |      |

| I <sub>CC1</sub> | Logic supply current           |    | I <sub>O</sub> = 0       | All outputs at low level         |                        | 35                     | 60   | mA   |

| .001             | 20g.0 0app.y 0a.10.11          |    | 10 - 0                   | All outputs at high impedance    |                        | 8                      | 24   |      |

|                  |                                |    |                          | All outputs at high level        |                        | 14                     | 24   |      |

| I <sub>CC2</sub> | Output supply current          |    | I <sub>O</sub> = 0       | All outputs at low level         |                        | 2                      | 6    | mA   |

| 'GG2             | Super supply surroin           |    | 10 = 0                   | All outputs at high impedance    |                        | 2                      | 4    |      |

#### 6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted) V<sub>CC1</sub> = 5 V, V<sub>CC2</sub> = 24 V, T<sub>A</sub> = 25°C

|                  | PARAMETER                          |                       | TEST CONDITIONS        | MIN                      | TYP | MAX | UNIT |  |

|------------------|------------------------------------|-----------------------|------------------------|--------------------------|-----|-----|------|--|

|                  | Propagation delay time, low-to-    | L293NE, L293DNE       |                        |                          | 800 |     | nc   |  |

| t <sub>PLH</sub> | high-level output from A input     | L293DWP, L293N L293DN |                        |                          | 750 |     | ns   |  |

|                  | Propagation delay time, high-to-   | L293NE, L293DNE       |                        |                          | 400 |     |      |  |

| t <sub>PHL</sub> | low-level output from A input      | L293DWP, L293N L293DN | $C_1 = 30 \text{ pF},$ |                          | 200 |     | ns   |  |

|                  | Transition time, low-to-high-level | L293NE, L293DNE       | See Figure 2           |                          | 300 |     |      |  |

| t <sub>TLH</sub> | output                             | L293DWP, L293N L293DN |                        | 750 ns 400 ns L = 30 pF, |     |     |      |  |

|                  | Transition time, high-to-low-level | L293NE, L293DNE       |                        |                          | 300 |     |      |  |

| t <sub>THL</sub> | output                             | L293DWP, L293N L293DN |                        |                          | 350 |     | ns   |  |

# 6.7 Typical Characteristics

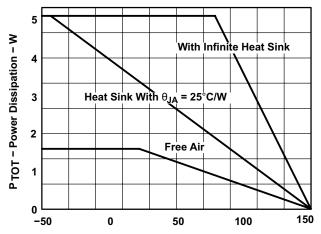

$T_A$  – Ambient Temperature – °C Figure 1. Maximum Power Dissipation vs Ambient Temperature

Copyright © 1986–2016, Texas Instruments Incorporated

#### 7 Parameter Measurement Information

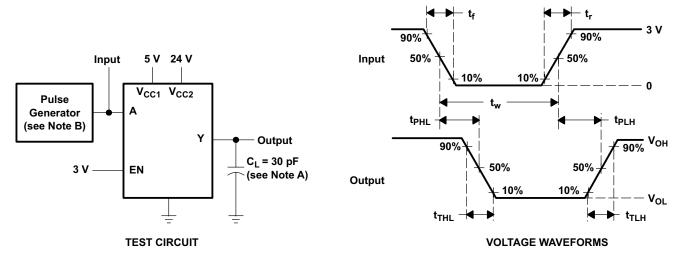

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

B. The pulse generator has the following characteristics:  $t_r \le 10$  ns,  $t_f \le 10$  ns,  $t_w = 10$   $\mu$ s, PRR = 5 kHz,  $Z_O = 50$   $\Omega$ .

Figure 2. Test Circuit and Voltage Waveforms

#### 8 Detailed Description

#### 8.1 Overview

The L293 and L293D are quadruple high-current half-H drivers. These devices are designed to drive a wide array of inductive loads such as relays, solenoids, DC and bipolar stepping motors, as well as other high-current and high-voltage loads. All inputs are TTL compatible and tolerant up to 7 V.

Each output is a complete totem-pole drive circuit, with a Darlington transistor sink and a pseudo-Darlington source. Drivers are enabled in pairs, with drivers 1 and 2 enabled by 1,2EN and drivers 3 and 4 enabled by 3,4EN. When an enable input is high, the associated drivers are enabled, and their outputs are active and in phase with their inputs. When the enable input is low, those drivers are disabled, and their outputs are off and in the high-impedance state. With the proper data inputs, each pair of drivers forms a full-H (or bridge) reversible drive suitable for solenoid or motor applications.

On the L293, external high-speed output clamp diodes should be used for inductive transient suppression. On the L293D, these diodes are integrated to reduce system complexity and overall system size. A  $V_{CC1}$  terminal, separate from  $V_{CC2}$ , is provided for the logic inputs to minimize device power dissipation. The L293 and L293D are characterized for operation from 0°C to 70°C.

#### 8.2 Functional Block Diagram

Output diodes are internal in L293D.

#### 8.3 Feature Description

The L293x has TTL-compatible inputs and high voltage outputs for inductive load driving. Current outputs can get up to 2 A using the L293.

#### 8.4 Device Functional Modes

Table 1 lists the fuctional modes of the L293x.

Table 1. Function Table (Each Driver)(1)

| INPU | OUTPUT (Y) |   |

|------|------------|---|

| Α    | A EN       |   |

| Н    | Н          | Н |

| L    | Н          | L |

| X    | L          | Z |

- (1) H = high level, L = low level, X = irrelevant, Z = high impedance (off)

(2) In the thermal shutdown mode, the output is in the high-impedance state, regardless of the input levels.

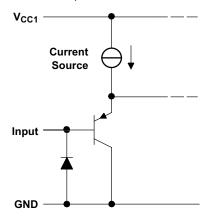

Figure 3. Schematic of Inputs for the L293x

Figure 4. Schematic of Outputs for the L293

Figure 5. Schematic of Outputs for the L293D

# 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

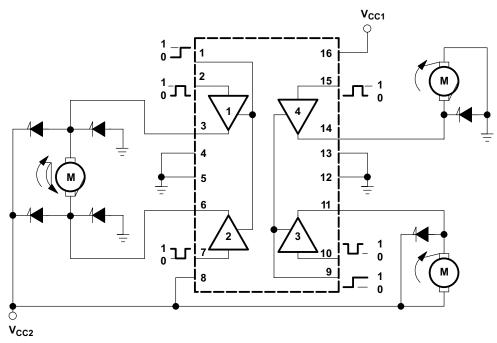

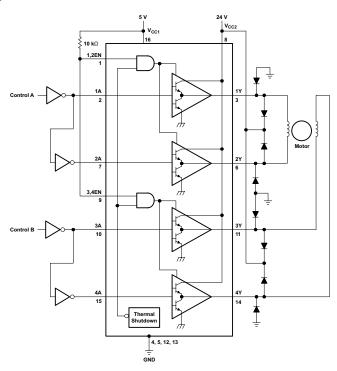

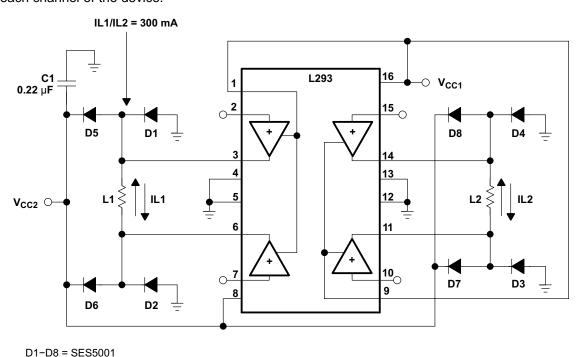

A typical application for the L293 device is driving a two-phase motor. Below is an example schematic displaying how to properly connect a two-phase motor to the L293 device.

Provide a 5-V supply to  $V_{CC1}$  and valid logic input levels to data and enable inputs.  $V_{CC2}$  must be connected to a power supply capable of supplying the needed current and voltage demand for the loads connected to the outputs.

#### 9.2 Typical Application

Figure 6. Two-Phase Motor Driver (L293)

#### 9.2.1 Design Requirements

The design techniques in the application above as well as the applications below should fall within the following design requirements.

- 1. V<sub>CC1</sub> should fall within the limits described in the *Recommended Operating Conditions*.

- 2. V<sub>CC2</sub> should fall within the limits described in the Recommended Operating Conditions.

- 3. The current per channel should not exceed 1 A for the L293 (600mA for the L293D).

#### 9.2.2 Detailed Design Procedure

When designing with the L293 or L293D, careful consideration should be made to ensure the device does not exceed the operating temperature of the device. Proper heatsinking will allow for operation over a larger range of current per channel. Refer to the *Power Supply Recommendations* as well as the *Layout Example*.

Product Folder Links: L293 L293D

#### **Typical Application (continued)**

#### 9.2.3 Application Curve

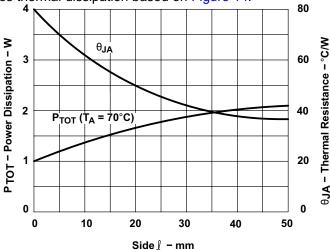

Refer to *Power Supply Recommendations* for additional information with regards to appropriate power dissipation. Figure 7 describes thermal dissipation based on Figure 14.

Figure 7. Maximum Power and Junction vs Thermal Resistance

#### 9.3 System Examples

#### 9.3.1 L293D as a Two-Phase Motor Driver

Figure 8 below depicts a typical setup for using the L293D as a two-phase motor driver. Refer to the *Recommended Operating Conditions* when considering the appropriate input high and input low voltage levels to enable each channel of the device.

Figure 8. Two-Phase Motor Driver (L293D)

#### System Examples (continued)

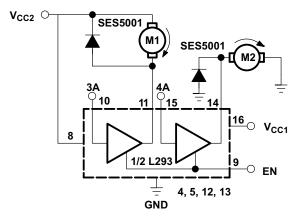

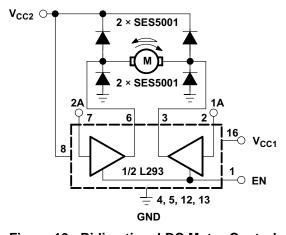

#### 9.3.2 DC Motor Controls

Figure 9 and Figure 10 below depict a typical setup for using the L293 device as a controller for DC motors. Note that the L293 device can be used as a simple driver for a motor to turn on and off in one direction, and can also be used to drive a motor in both directions. Refer to the function tables below to understand unidirectional vs bidirectional motor control. Refer to the *Recommended Operating Conditions* when considering the appropriate input high and input low voltage levels to enable each channel of the device.

Connections to ground and to supply voltage

Figure 9. DC Motor Controls

**Table 2. Unidirectional DC Motor Control**

| EN | 3A | M1 <sup>(1)</sup>       | 4A | M2                      |

|----|----|-------------------------|----|-------------------------|

| Н  | Н  | Fast motor stop         | Н  | Run                     |

| Н  | L  | run                     | L  | Fast motor stop         |

| L  | X  | Free-running motor stop | Х  | Free-running motor stop |

(1) L = low, H = high, X = don't care

Figure 10. Bidirectional DC Motor Control

**Table 3. Bidrectional DC Motor Control**

| EN | 1A | 2A | FUNCTION <sup>(1)</sup> |

|----|----|----|-------------------------|

| Н  | L  | Н  | Turn right              |

| Н  | Н  | L  | Turn left               |

(1) L = low, H = high, X = don't care

**Table 3. Bidrectional DC Motor Control (continued)**

| EN | 1A | 2A | FUNCTION <sup>(1)</sup> |

|----|----|----|-------------------------|

| Н  | L  | L  | Fast motor stop         |

| Н  | Н  | Н  | Fast motor stop         |

| L  | X  | X  | Free-running motor stop |

#### 9.3.3 Bipolar Stepping-Motor Control

Figure 11 below depicts a typical setup for using the L293D as a two-phase motor driver. Refer to the *Recommended Operating Conditions* when considering the appropriate input high and input low voltage levels to enable each channel of the device.

Figure 11. Bipolar Stepping-Motor Control

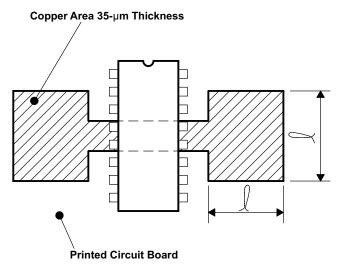

#### 10 Power Supply Recommendations

$V_{\rm CC1}$  is 5 V ± 0.5 V and  $V_{\rm CC2}$  can be same supply as  $V_{\rm CC1}$  or a higher voltage supply with peak voltage up to 36 V. Bypass capacitors of 0.1 uF or greater should be used at  $V_{\rm CC1}$  and  $V_{\rm CC2}$  pins. There are no power up or power down supply sequence order requirements.

Properly heatsinking the L293 when driving high-current is critical to design. The Rthj-amp of the L293 can be reduced by soldering the GND pins to a suitable copper area of the printed circuit board or to an external heat sink.

Figure 14 shows the maximum package power PTOT and the  $\theta$ JA as a function of the side of two equal square copper areas having a thickness of 35  $\mu$ m (see Figure 14). In addition, an external heat sink can be used (see Figure 12).

During soldering, the pin temperature must not exceed 260°C, and the soldering time must not exceed 12 seconds.

The external heatsink or printed circuit copper area must be connected to electrical ground.

Figure 12. External Heat Sink Mounting Example ( $\theta_{JA} = 25^{\circ}$ C/W)

Copyright © 1986–2016, Texas Instruments Incorporated

## 11 Layout

### 11.1 Layout Guidelines

Place the device near the load to keep output traces short to reduce EMI. Use solid vias to transfer heat from ground pins to ground plane of the printed-circuit-board.

#### 11.2 Layout Example

Figure 13. Layout Diagram

Figure 14. Example of Printed-Circuit-Board Copper Area (Used as Heat Sink)

#### 12 Device and Documentation Support

#### 12.1 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 4. Related Links

| PARTS | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |  |

|-------|----------------|--------------|---------------------|---------------------|---------------------|--|

| L293  | Click here     | Click here   | Click here          | Click here          | Click here          |  |

| L293D | Click here     | Click here   | Click here          | Click here          | Click here          |  |

#### 12.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.3 Trademarks

E2E is a trademark of Texas Instruments.

Copyright © 1986-2016, Texas Instruments Incorporated

All other trademarks are the property of their respective owners.

#### 12.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 12.5 Glossary

SLYZ022 — TI Glossarv.

This glossary lists and explains terms, acronyms, and definitions.

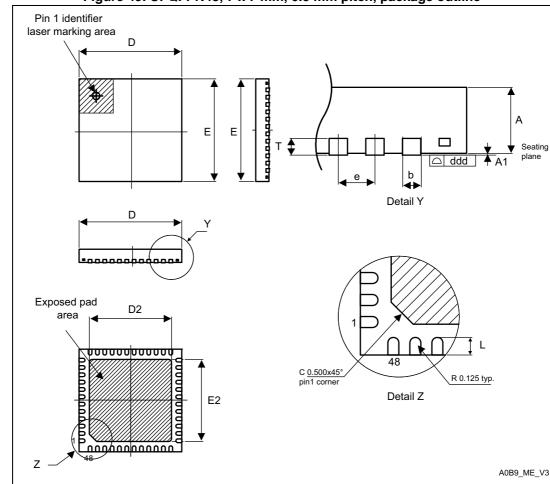

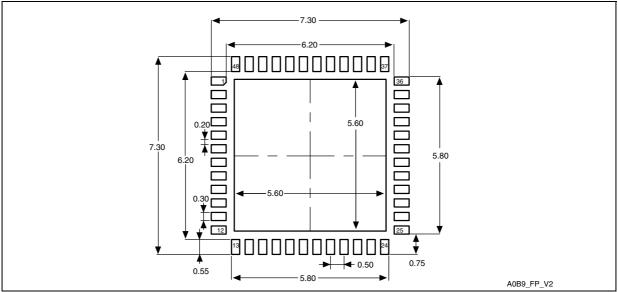

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

17-Mar-2017

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan          | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|-------------------|------------------|--------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |                   | ` '              |                    |              | ` '                  |         |

| L293DNE          | ACTIVE | PDIP         | NE                 | 16   | 25             | Pb-Free<br>(RoHS) | CU NIPDAU        | N / A for Pkg Type | 0 to 70      | L293DNE              | Samples |

| L293DNEE4        | ACTIVE | PDIP         | NE                 | 16   | 25             | Pb-Free<br>(RoHS) | CU NIPDAU        | N / A for Pkg Type | 0 to 70      | L293DNE              | Samples |

| L293NE           | ACTIVE | PDIP         | NE                 | 16   | 25             | Pb-Free<br>(RoHS) | CU NIPDAU        | N / A for Pkg Type | 0 to 70      | L293NE               | Samples |

| L293NEE4         | ACTIVE | PDIP         | NE                 | 16   | 25             | Pb-Free<br>(RoHS) | CU NIPDAU        | N / A for Pkg Type | 0 to 70      | L293NE               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

### PACKAGE OPTION ADDENDUM

17-Mar-2017

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### IMPORTANT NOTICE

Texas Instruments Incorporated (TI) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI's published terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products that TI has qualified and released to market. Additional terms may apply to the use or sale of other types of TI products and services.

Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyers and others who are developing systems that incorporate TI products (collectively, "Designers") understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications (and of all TI products used in or for Designers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Designer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any applications that include TI products, Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.

TI's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using TI Resources in any way, Designer (individually or, if Designer is acting on behalf of a company, Designer's company) agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

Designer is authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949 and ISO 26262), TI is not responsible for any failure to meet such industry standard requirements.

Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Designers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

TI may expressly designate certain products as completing a particular qualification (e.g., Q100, Military Grade, or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers' own risk. Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's non-compliance with the terms and provisions of this Notice.

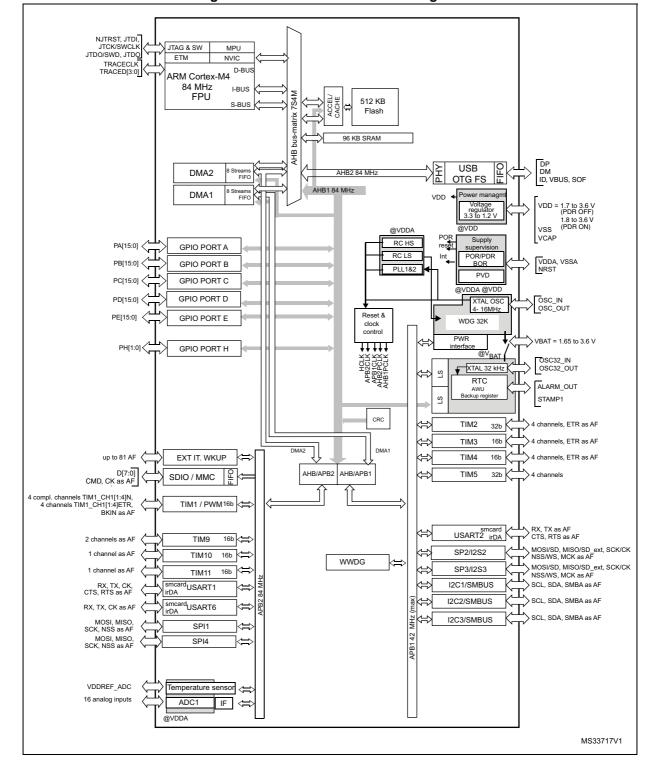

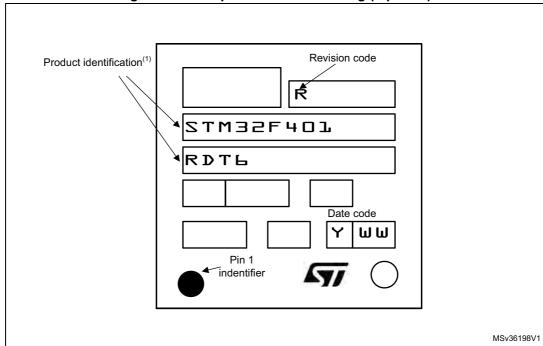

# STM32F401xD STM32F401xE

# ARM® Cortex®-M4 32b MCU+FPU, 105 DMIPS, 512KB Flash/96KB RAM, 11 TIMs, 1 ADC, 11 comm. interfaces

**Datasheet - production data**

#### **Features**

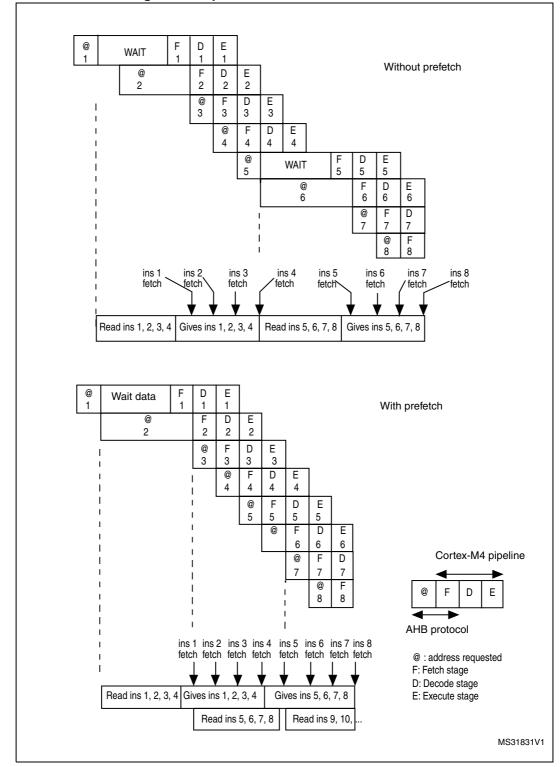

- Core: ARM<sup>®</sup> 32-bit Cortex<sup>®</sup>-M4 CPU with FPU, Adaptive real-time accelerator (ART Accelerator<sup>™</sup>) allowing 0-wait state execution from Flash memory, frequency up to 84 MHz, memory protection unit, 105 DMIPS/1.25 DMIPS/MHz (Dhrystone 2.1), and DSP instructions

- Memories

- up to 512 Kbytes of Flash memory

- up to 96 Kbytes of SRAM

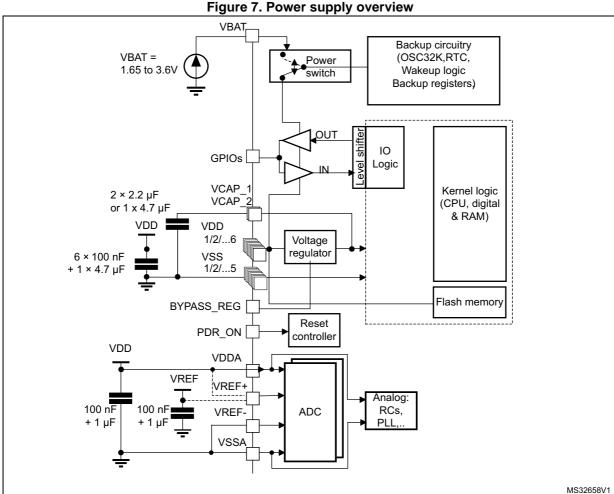

- Clock, reset and supply management

- 1.7 V to 3.6 V application supply and I/Os

- POR, PDR, PVD and BOR

- 4-to-26 MHz crystal oscillator

- Internal 16 MHz factory-trimmed RC

- 32 kHz oscillator for RTC with calibration

- Internal 32 kHz RC with calibration

- · Power consumption

- Run: 146 µA/MHz (peripheral off)

- Stop (Flash in Stop mode, fast wakeup time): 42 μA Typ @ 25C; 65 μA max @ 25 °C

- Stop (Flash in Deep power down mode, fast wakeup time): down to 10 μA @ 25 °C; 30 μA max @25 °C

- Standby: 2.4  $\mu$ A @25 °C / 1.7 V without RTC; 12  $\mu$ A @85 °C @1.7 V

- V<sub>BAT</sub> supply for RTC: 1  $\mu$ A @25 °C

- 1x12-bit, 2.4 MSPS A/D converter: up to 16 channels

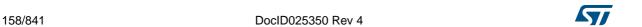

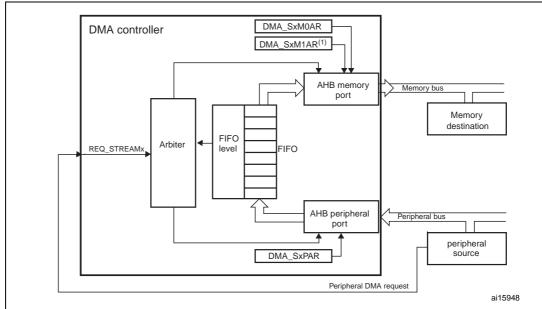

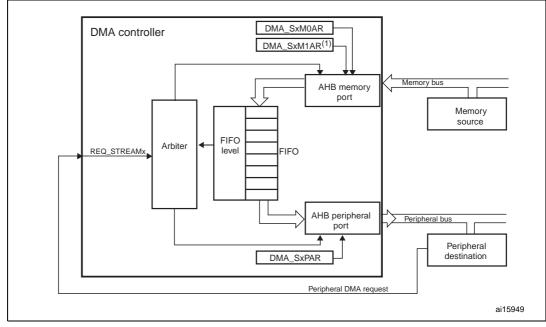

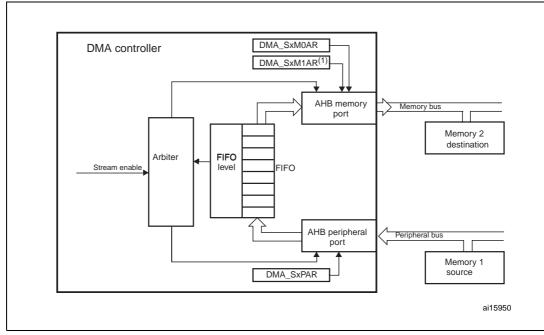

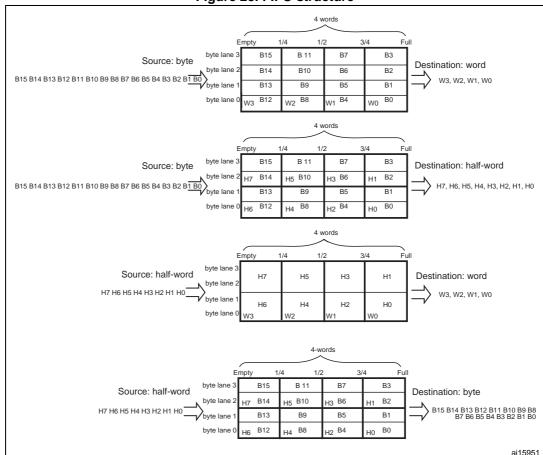

- General-purpose DMA: 16-stream DMA controllers with FIFOs and burst support

- Up to 11 timers: up to six 16-bit, two 32-bit timers up to 84 MHz, each with up to four IC/OC/PWM or pulse counter and quadrature (incremental) encoder input, two watchdog timers (independent and window) and a SysTick timer

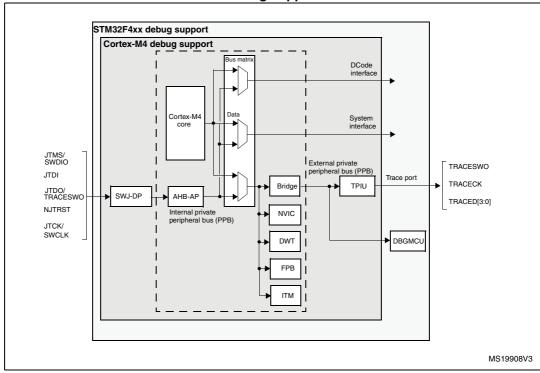

- Debug mode

- Serial wire debug (SWD) & JTAG interfaces

- Cortex<sup>®</sup>-M4 Embedded Trace Macrocell™

- Up to 81 I/O ports with interrupt capability

- Up to 78 fast I/Os up to 42 MHz

- All I/O ports are 5 V-tolerant

- Up to 12 communication interfaces

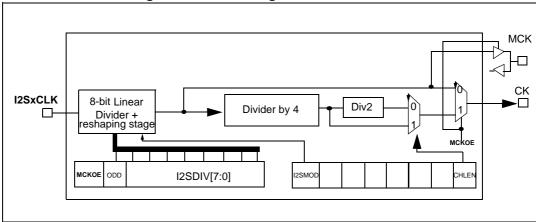

- Up to 3 x I<sup>2</sup>C interfaces (SMBus/PMBus)

- Up to 3 USARTs (2 x 10.5 Mbit/s, 1 x 5.25 Mbit/s), ISO 7816 interface, LIN, IrDA, modem control)

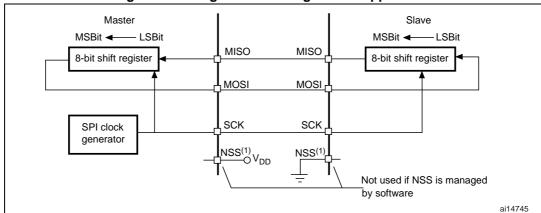

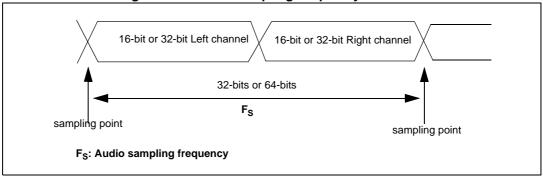

- Up to 4 SPIs (up to 42Mbit/s at f<sub>CPU</sub> = 84 MHz), SPI2 and SPI3 with muxed full-duplex I<sup>2</sup>S to achieve audio class accuracy via internal audio PLL or external clock

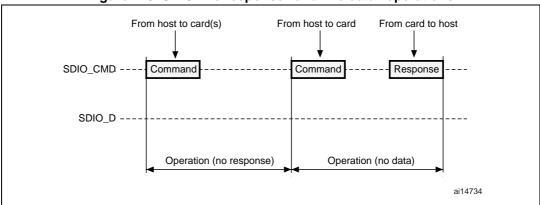

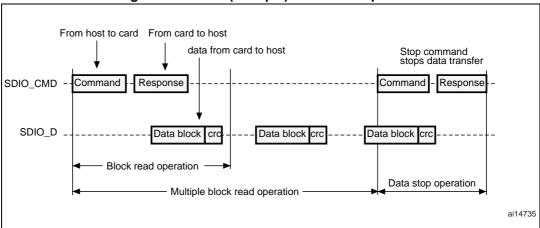

- SDIO interface

- Advanced connectivity: USB 2.0 full-speed device/host/OTG controller with on-chip PHY

- CRC calculation unit

- 96-bit unique ID

- RTC: subsecond accuracy, hardware calendar

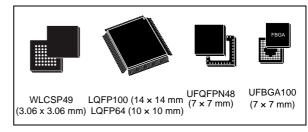

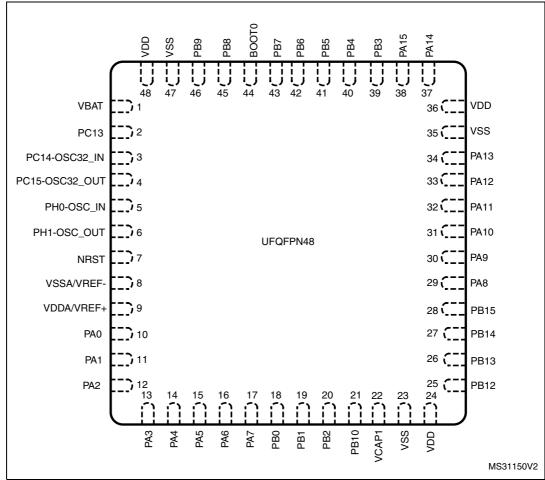

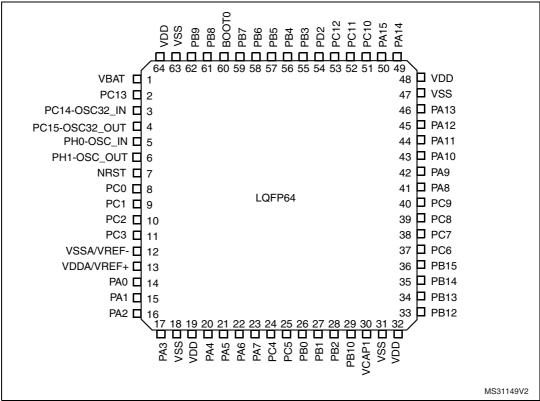

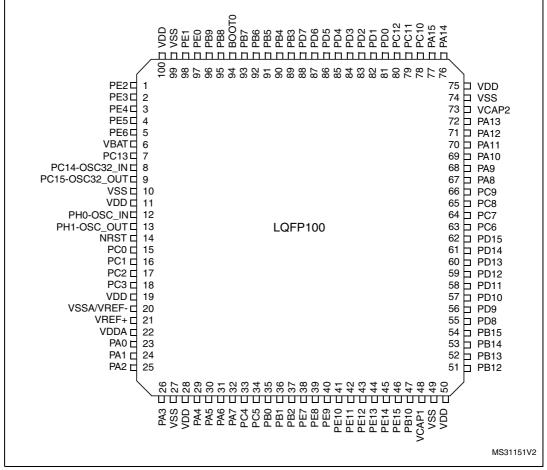

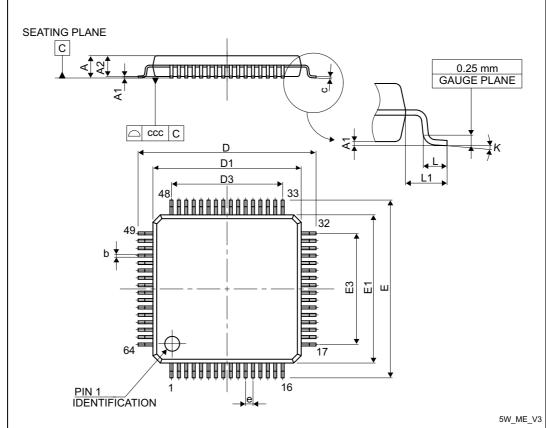

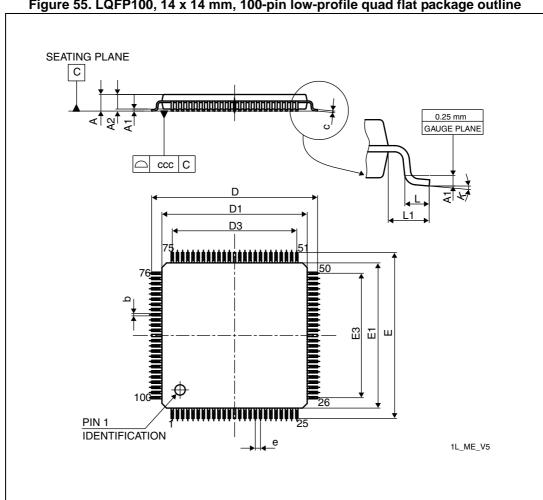

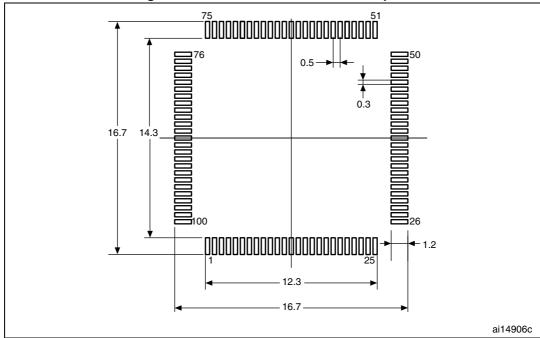

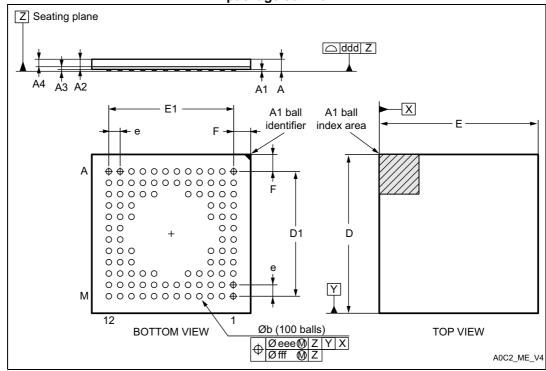

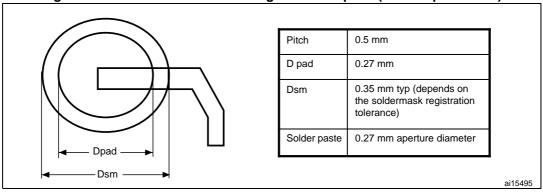

- All packages (WLCSP49, LQFP64/100, UFQFPN48, UFBGA100) are ECOPACK<sup>®</sup>2

Table 1. Device summary

| Reference   | Part number                              |

|-------------|------------------------------------------|

| STM32F401xD | STM32F401CD,<br>STM32F401RD, STM32F401VD |

| STM32F401xE | STM32F401CE,<br>STM32F401RE, STM32F401VE |

# **Contents**

| 1 | Intro | Introduction9                                                                |  |  |  |  |  |  |  |  |  |

|---|-------|------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 2 | Desc  | ription                                                                      |  |  |  |  |  |  |  |  |  |

|   | 2.1   | Compatibility with STM32F4 series                                            |  |  |  |  |  |  |  |  |  |

| 3 | Func  | Functional overview 1                                                        |  |  |  |  |  |  |  |  |  |

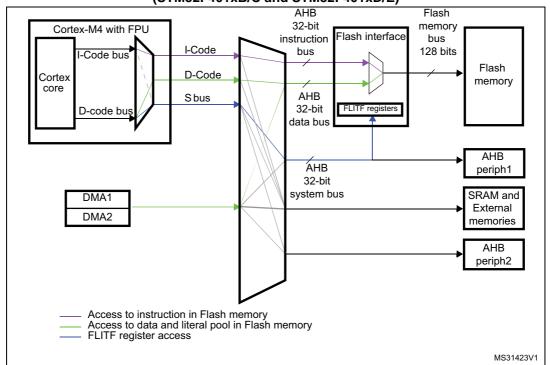

|   | 3.1   | ARM® Cortex®-M4 with FPU core with embedded Flash and SRAM 15                |  |  |  |  |  |  |  |  |  |

|   | 3.2   | Adaptive real-time memory accelerator (ART Accelerator™) 15                  |  |  |  |  |  |  |  |  |  |

|   | 3.3   | Memory protection unit                                                       |  |  |  |  |  |  |  |  |  |

|   | 3.4   | Embedded Flash memory                                                        |  |  |  |  |  |  |  |  |  |

|   | 3.5   | CRC (cyclic redundancy check) calculation unit                               |  |  |  |  |  |  |  |  |  |

|   | 3.6   | Embedded SRAM                                                                |  |  |  |  |  |  |  |  |  |

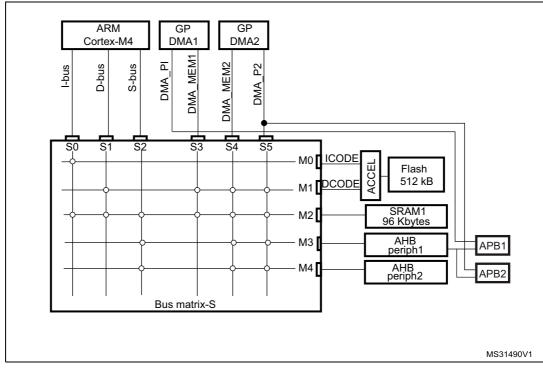

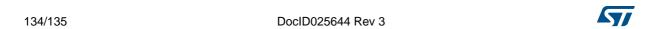

|   | 3.7   | Multi-AHB bus matrix                                                         |  |  |  |  |  |  |  |  |  |

|   | 3.8   | DMA controller (DMA)                                                         |  |  |  |  |  |  |  |  |  |

|   | 3.9   | Nested vectored interrupt controller (NVIC)                                  |  |  |  |  |  |  |  |  |  |

|   | 3.10  | External interrupt/event controller (EXTI)                                   |  |  |  |  |  |  |  |  |  |

|   | 3.11  | Clocks and startup                                                           |  |  |  |  |  |  |  |  |  |

|   | 3.12  | Boot modes                                                                   |  |  |  |  |  |  |  |  |  |

|   | 3.13  | Power supply schemes                                                         |  |  |  |  |  |  |  |  |  |

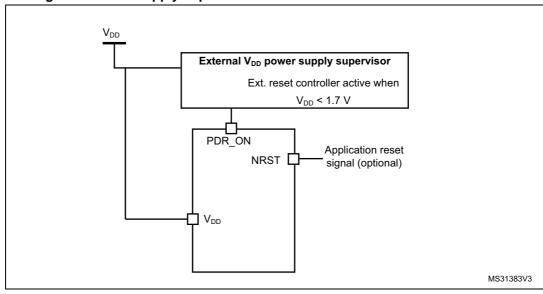

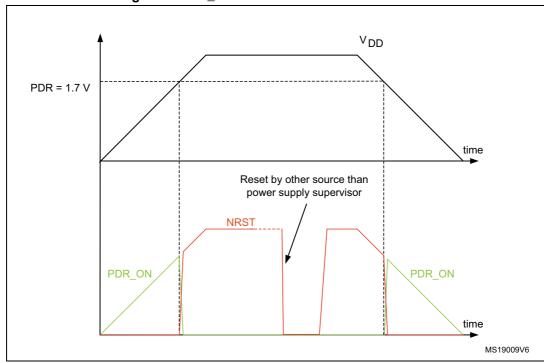

|   | 3.14  | Power supply supervisor                                                      |  |  |  |  |  |  |  |  |  |

|   |       | 3.14.1 Internal reset ON                                                     |  |  |  |  |  |  |  |  |  |

|   |       | 3.14.2 Internal reset OFF                                                    |  |  |  |  |  |  |  |  |  |

|   | 3.15  | Voltage regulator 21                                                         |  |  |  |  |  |  |  |  |  |

|   |       | 3.15.1 Regulator ON                                                          |  |  |  |  |  |  |  |  |  |

|   |       | 3.15.2 Regulator OFF                                                         |  |  |  |  |  |  |  |  |  |

|   |       | 3.15.3 Regulator ON/OFF and internal power supply supervisor availability 25 |  |  |  |  |  |  |  |  |  |

|   | 3.16  | Real-time clock (RTC) and backup registers                                   |  |  |  |  |  |  |  |  |  |

|   | 3.17  | Low-power modes                                                              |  |  |  |  |  |  |  |  |  |

|   | 3.18  | V <sub>BAT</sub> operation                                                   |  |  |  |  |  |  |  |  |  |

|   | 3.19  | Timers and watchdogs                                                         |  |  |  |  |  |  |  |  |  |

|   |       | 3.19.1 Advanced-control timers (TIM1)                                        |  |  |  |  |  |  |  |  |  |

|   |       | 3.19.2 General-purpose timers (TIMx)                                         |  |  |  |  |  |  |  |  |  |

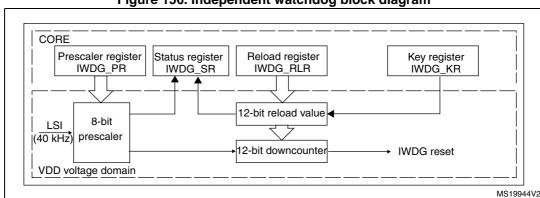

|        |                      | 3.19.3                                                                                                                           | Independent watchdog                                                                                                                                                                                                                                                                                                                     | 28                                                                                           |

|--------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|        |                      | 3.19.4                                                                                                                           | Window watchdog                                                                                                                                                                                                                                                                                                                          | 28                                                                                           |

|        |                      | 3.19.5                                                                                                                           | SysTick timer                                                                                                                                                                                                                                                                                                                            | 29                                                                                           |

|        | 3.20                 | Inter-in                                                                                                                         | ntegrated circuit interface (I2C)                                                                                                                                                                                                                                                                                                        | . 29                                                                                         |

|        | 3.21                 | Univer                                                                                                                           | sal synchronous/asynchronous receiver transmitters (USART) .                                                                                                                                                                                                                                                                             | . 29                                                                                         |

|        | 3.22                 | Serial <sub>l</sub>                                                                                                              | peripheral interface (SPI)                                                                                                                                                                                                                                                                                                               | . 30                                                                                         |

|        | 3.23                 | Inter-in                                                                                                                         | ntegrated sound (I <sup>2</sup> S)                                                                                                                                                                                                                                                                                                       | . 30                                                                                         |

|        | 3.24                 | Audio l                                                                                                                          | PLL (PLLI2S)                                                                                                                                                                                                                                                                                                                             | . 30                                                                                         |

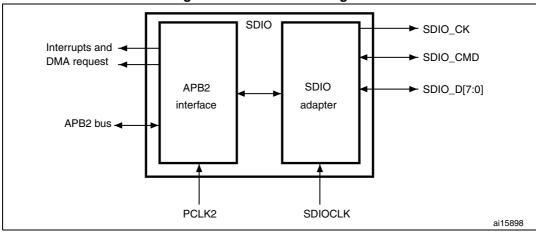

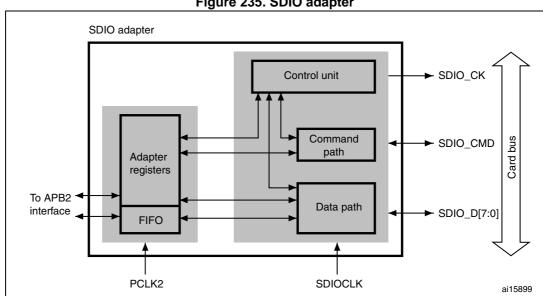

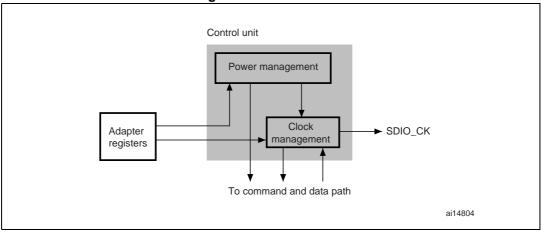

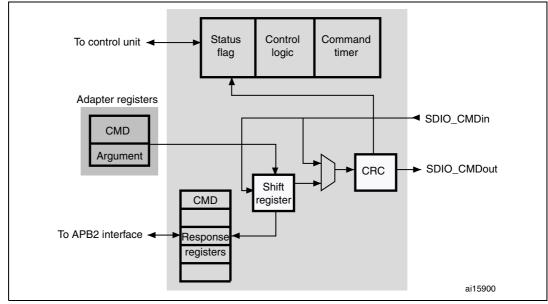

|        | 3.25                 | Secure                                                                                                                           | e digital input/output interface (SDIO)                                                                                                                                                                                                                                                                                                  | . 31                                                                                         |

|        | 3.26                 | Univer                                                                                                                           | sal serial bus on-the-go full-speed (OTG_FS)                                                                                                                                                                                                                                                                                             | . 31                                                                                         |

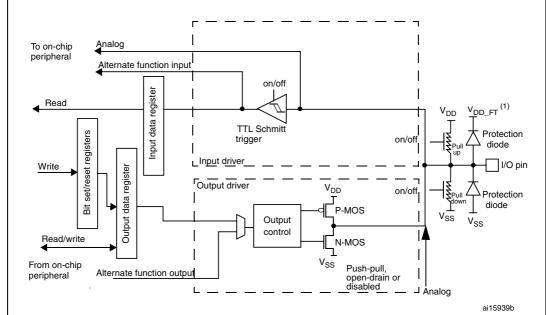

|        | 3.27                 | Genera                                                                                                                           | al-purpose input/outputs (GPIOs)                                                                                                                                                                                                                                                                                                         | . 31                                                                                         |

|        | 3.28                 | Analog                                                                                                                           | g-to-digital converter (ADC)                                                                                                                                                                                                                                                                                                             | . 31                                                                                         |

|        | 3.29                 | Tempe                                                                                                                            | erature sensor                                                                                                                                                                                                                                                                                                                           | . 32                                                                                         |

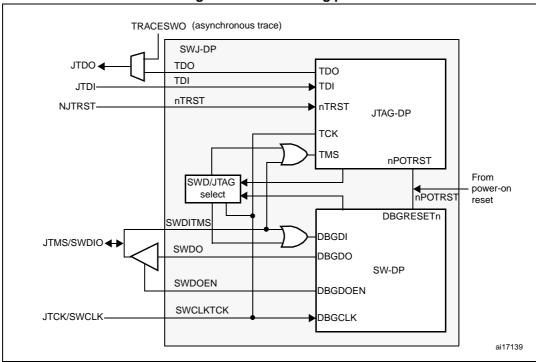

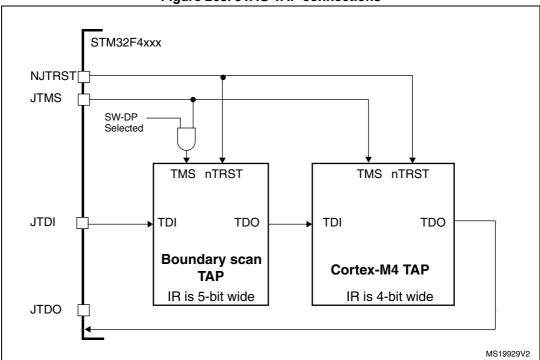

|        | 3.30                 | Serial v                                                                                                                         | wire JTAG debug port (SWJ-DP)                                                                                                                                                                                                                                                                                                            | . 32                                                                                         |

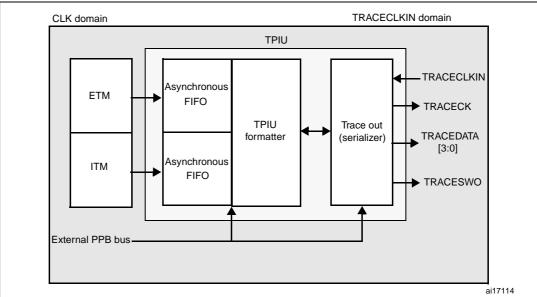

|        | 3.31                 |                                                                                                                                  | dded Trace Macrocell™                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|        |                      |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 4      | Pino                 | uts and                                                                                                                          | pin description                                                                                                                                                                                                                                                                                                                          | . 33                                                                                         |

| 4      |                      |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

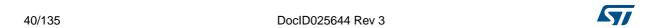

|        |                      | ory ma                                                                                                                           | pping                                                                                                                                                                                                                                                                                                                                    | . 51                                                                                         |

| 5      | Mem                  |                                                                                                                                  | pping                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 5      | Mem                  | rical ch                                                                                                                         |                                                                                                                                                                                                                                                                                                                                          | . 55                                                                                         |

| 5      | Mem<br>Elect         | rical ch                                                                                                                         | naracteristics                                                                                                                                                                                                                                                                                                                           | <b>. 55</b><br>. 55                                                                          |

| 5      | Mem<br>Elect         | t <b>rical ch</b><br>Param                                                                                                       | naracteristics eter conditions                                                                                                                                                                                                                                                                                                           | <b>. 55</b><br>. 55                                                                          |

| 5      | Mem<br>Elect         | rical ch<br>Param<br>6.1.1                                                                                                       | naracteristics                                                                                                                                                                                                                                                                                                                           | . <b>55</b><br>. 55<br>55                                                                    |

| 5      | Mem<br>Elect         | Param<br>6.1.1<br>6.1.2                                                                                                          | eter conditions                                                                                                                                                                                                                                                                                                                          | . <b>55</b> . 55 . 55 55                                                                     |

| 5      | Mem<br>Elect         | Param<br>6.1.1<br>6.1.2<br>6.1.3                                                                                                 | eter conditions                                                                                                                                                                                                                                                                                                                          | . 55<br>. 55<br>55<br>55<br>55                                                               |

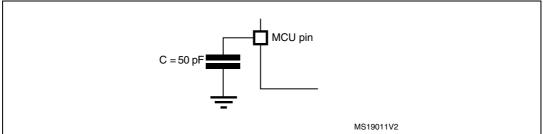

| 5      | Mem<br>Elect         | Param<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                                                        | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor                                                                                                                                                                                                                                           | . 55<br>. 55<br>. 55<br>. 55<br>. 55<br>. 55                                                 |

| 5      | Mem<br>Elect         | Param<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                                               | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage                                                                                                                                                                                                                        | . 55<br>. 55<br>. 55<br>. 55<br>. 55<br>. 56                                                 |

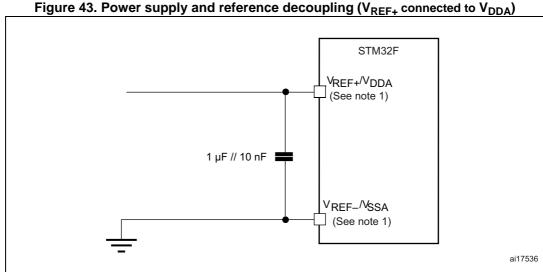

| 5      | Mem<br>Elect         | Param<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7                                                             | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme                                                                                                                                                                                                   | . <b>55</b> . 55 . 55 . 55 . 55 . 55 . 56 . 57                                               |

| 5      | Mem<br>Elect<br>6.1  | Param<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolu                                                   | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement                                                                                                                                                                  | . 55<br>. 55<br>. 55<br>. 55<br>. 55<br>. 55<br>. 56<br>. 57                                 |

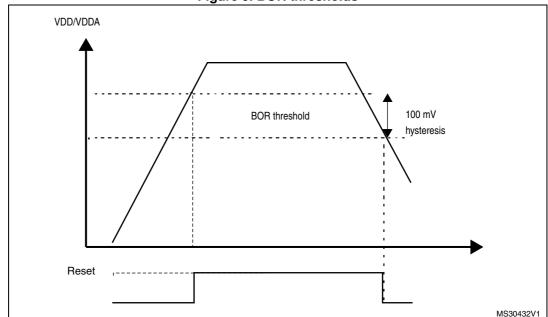

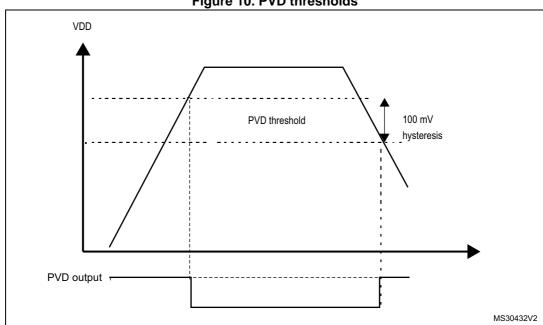

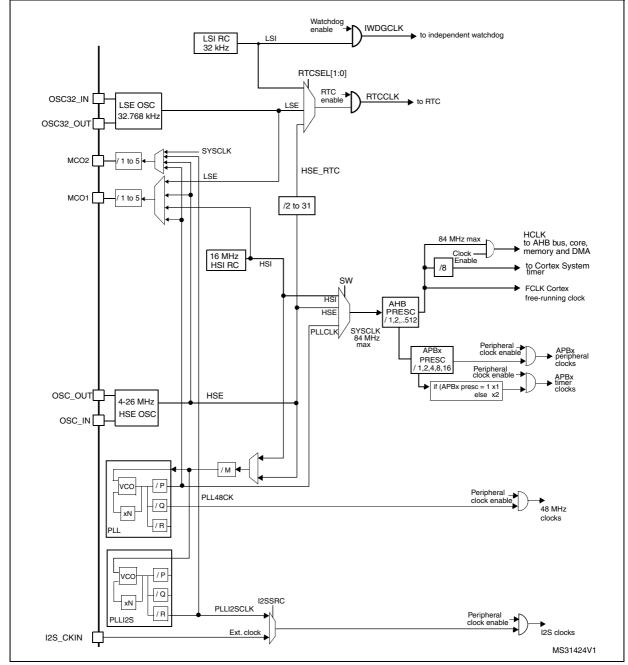

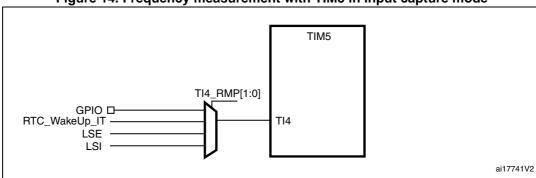

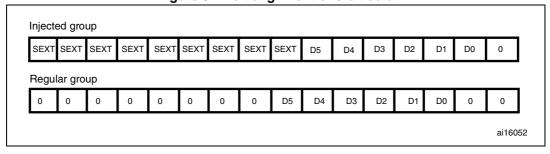

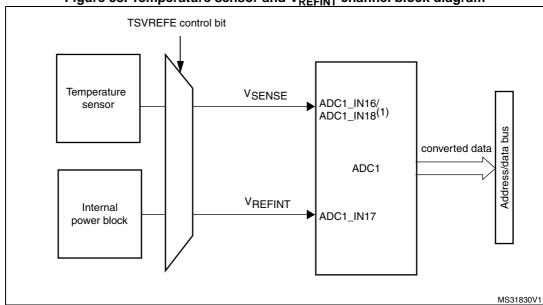

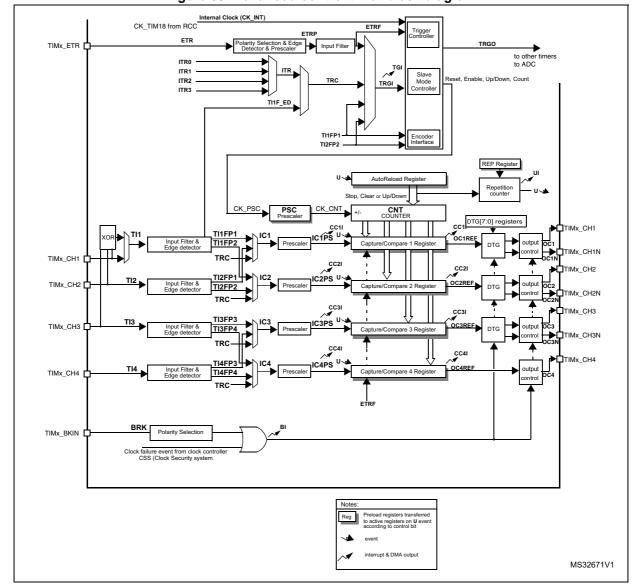

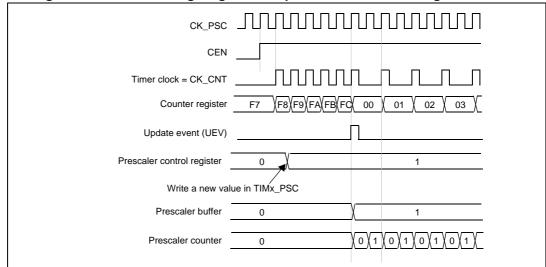

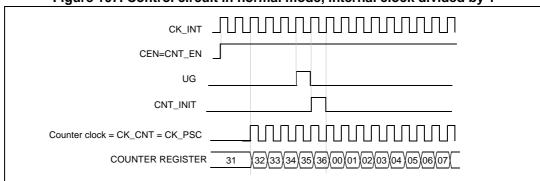

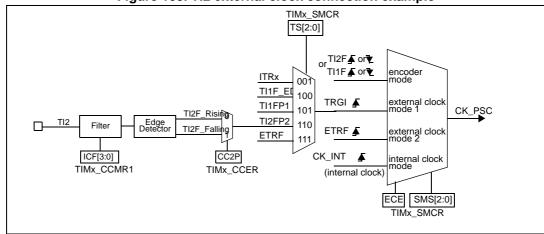

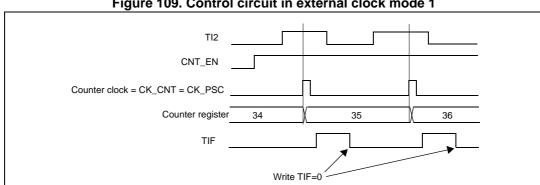

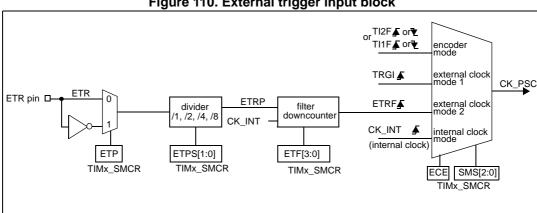

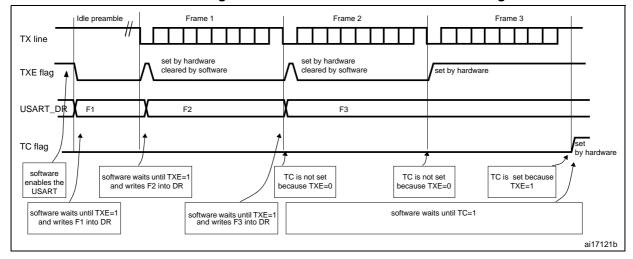

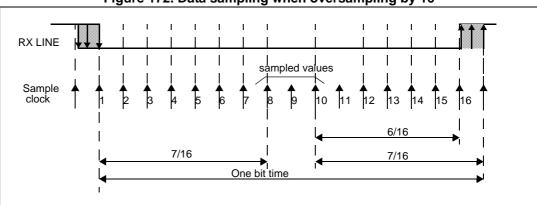

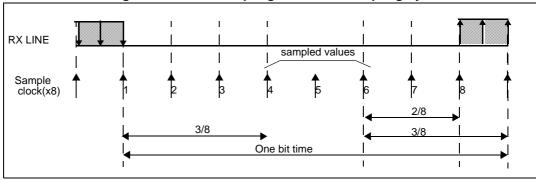

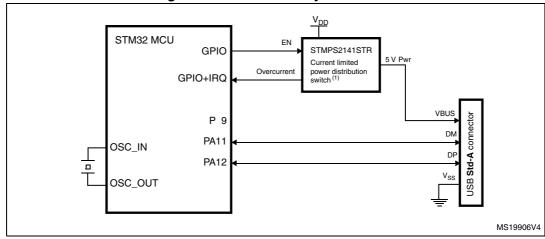

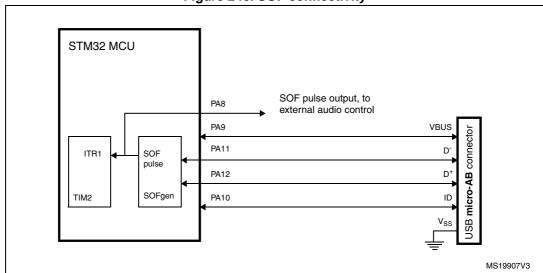

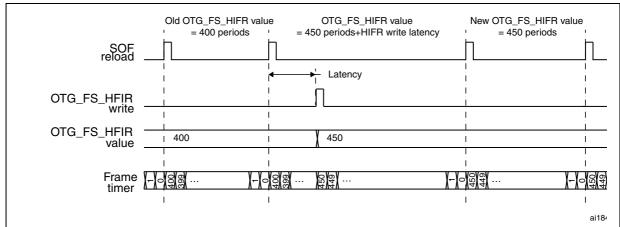

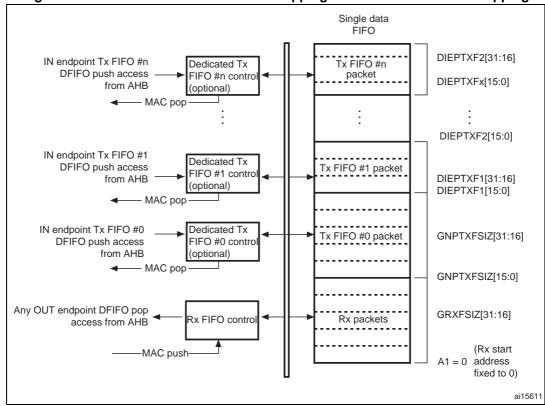

| 5      | <b>Mem Elect</b> 6.1 | Param<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolu                                                   | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  ste maximum ratings                                                                                                                                             | . 55<br>. 55<br>. 55<br>. 55<br>. 55<br>. 55<br>. 56<br>. 57<br>. 58<br>. 60                 |